Pentium (original) - Pentium (original)

| |

| Información general | |

|---|---|

| Lanzado | 22 de marzo de 1993 |

| Interrumpido | 15 de febrero de 2000 |

| Rendimiento | |

| Max. Frecuencia de reloj de la CPU | 60–300 MHz |

| Velocidades FSB | 50–66 MHz |

| Cache | |

| Caché L1 | 16–32 KiB |

| Arquitectura y clasificación | |

| Arquitectura | P5 ( IA-32 ) |

| Instrucciones | MMX |

| Especificaciones físicas | |

| Enchufe (s) | |

| Productos, modelos, variantes | |

| Modelo (s) | |

| Historia | |

| Predecesor | Intel 80486 |

| Sucesor | P6 , Pentium II |

El microprocesador Pentium fue presentado por Intel el 22 de marzo de 1993 como la primera CPU de la marca Pentium . Era un conjunto de instrucciones compatible con el 80486, pero era un diseño de microarquitectura nuevo y muy diferente. El Pentium P5 fue la primera microarquitectura x86 superescalar y el primer microprocesador superescalar del mundo en producción en masa. Incluía canalizaciones de números enteros duales , una unidad de punto flotante más rápida , un bus de datos más amplio , cachés de código y datos separados , y muchas otras técnicas y características para mejorar el rendimiento y respaldar la seguridad, el cifrado y el multiprocesamiento para estaciones de trabajo y servidores.

Considerada la quinta generación principal en la línea de procesadores compatibles con 8086, su implementación y microarquitectura se denominó P5 . Al igual que con todos los procesadores nuevos de Intel desde Pentium, se agregaron algunas instrucciones nuevas para mejorar el rendimiento para tipos específicos de cargas de trabajo.

El Pentium fue el primer Intel x86 en incorporar un sólido soporte de hardware para multiprocesamiento similar al de las grandes computadoras centrales de IBM. Intel trabajó en estrecha colaboración con IBM para definir esta capacidad y luego Intel la diseñó en la microarquitectura P5. Esta nueva capacidad estaba ausente en generaciones anteriores de x86 y copias x86 de la competencia.

Para realizar su mayor potencial, los compiladores tuvieron que optimizarse para explotar el paralelismo de nivel de instrucción proporcionado por las nuevas canalizaciones duales superescalares y las aplicaciones debían recompilarse. Intel dedicó un esfuerzo y recursos sustanciales a trabajar con los proveedores de herramientas de desarrollo y las principales empresas de proveedores de software independientes (ISV) y sistemas operativos (SO) para optimizar sus productos para Pentium antes del lanzamiento del producto.

En octubre de 1996, se introdujo el Pentium MMX similar , que complementa la misma microarquitectura básica con el conjunto de instrucciones MMX , cachés más grandes y algunas otras mejoras.

Entre los competidores se incluían las familias Motorola 68040 , Motorola 68060 , PowerPC 601 , SPARC , MIPS , Alpha , la mayoría de las cuales también utilizaron una configuración superescalar de canalización de instrucción dual en orden en algún momento.

Intel descontinuó los procesadores Pentium P5 (vendidos como un producto más barato desde el Pentium II de 1997) a principios de 2000 a favor del procesador Celeron , que también había reemplazado a la marca 80486 .

Desarrollo

La microarquitectura P5 fue diseñada por el mismo equipo de Santa Clara que diseñó el 386 y el 486. El trabajo de diseño se inició en 1989; el equipo decidió utilizar una arquitectura superescalar , con caché en chip, punto flotante y predicción de ramas. El diseño preliminar se simuló con éxito por primera vez en 1990, seguido del trazado del diseño. En ese momento, el equipo tenía varias docenas de ingenieros. El diseño se grabó o se transfirió a silicio en abril de 1992, momento en el que comenzaron las pruebas beta. A mediados de 1992, el equipo P5 tenía 200 ingenieros. Al principio, Intel planeó demostrar el P5 en junio de 1992 en la feria comercial PC Expo y anunciar formalmente el procesador en septiembre de 1992, pero los problemas de diseño obligaron a cancelar la demostración y la introducción oficial del chip se retrasó hasta la primavera. de 1993.

John H. Crawford , arquitecto jefe del 386 original, co-dirigió el diseño del P5, junto con Donald Alpert, quien dirigió el equipo de arquitectura. Dror Avnon dirigió el diseño de la FPU. Vinod K. Dham fue director general del grupo P5.

El proyecto de arquitectura multinúcleo Larrabee de Intel utiliza un núcleo de procesador derivado de un núcleo P5 (P54C), aumentado por múltiples subprocesos , instrucciones de 64 bits y una unidad de procesamiento vectorial de 16 anchos . La microarquitectura Bonnell de baja potencia de Intel empleada en los primeros núcleos de los procesadores Atom también utiliza una tubería dual en orden similar a P5.

Intel usó el nombre Pentium en lugar de 80586, porque descubrió que los números no pueden ser marcas registradas .

Mejoras sobre el i486

La microarquitectura P5 aporta varios avances importantes sobre la arquitectura i486 anterior.

-

Rendimiento :

- Arquitectura superescalar : el Pentium tiene dos rutas de datos (canalizaciones) que le permiten completar dos instrucciones por ciclo de reloj en muchos casos. La tubería principal (U) puede manejar cualquier instrucción, mientras que la otra (V) puede manejar las instrucciones simples más comunes. Algunos defensores de la computadora con conjunto de instrucciones reducido (RISC) habían argumentado que el conjunto de instrucciones x86 "complicado" probablemente nunca sería implementado por una microarquitectura estrechamente interconectada , y mucho menos por un diseño de doble conducto. El 486 y el Pentium demostraron que esto era posible y factible.

- El bus de datos externo de 64 bits duplica la cantidad de información posible para leer o escribir en cada acceso a la memoria y, por lo tanto, permite que el Pentium cargue su caché de código más rápido que el 80486; También permite un acceso y almacenamiento más rápidos de datos FPU x87 de 64 y 80 bits .

- La separación de cachés de código y datos reduce los conflictos de lectura / escritura de operaciones y operaciones en comparación con el 486. Para reducir el tiempo de acceso y el costo de implementación, ambos son asociativos de 2 vías , en lugar del caché de 4 vías único del 486. A La mejora relacionada en el Pentium es la capacidad de leer un bloque contiguo del caché de código incluso cuando está dividido entre dos líneas de caché (al menos 17 bytes en el peor de los casos).

- Unidad de punto flotante mucho más rápida . Algunas instrucciones mostraron una mejora enorme, sobre todo FMUL, con un rendimiento hasta 15 veces mayor que en el 80486 FPU. El Pentium también puede ejecutar una instrucción FXCH ST (x) en paralelo con una instrucción FPU ordinaria (aritmética o de carga / almacenamiento).

- Sumadores de dirección de cuatro entradas permite el Pentium a reducir aún más el cálculo de la dirección de latencia en comparación con el 80486. El Pentium puede calcular modos de direccionamiento completos con segmento-base + de base a registrar + registro escalado + inmediata desplazamiento en un solo ciclo; el 486 tiene un sumador de direcciones de tres entradas solamente y, por lo tanto, debe dividir dichos cálculos entre dos ciclos.

- El microcódigo puede emplear ambos canales para permitir que las instrucciones de repetición automática, como REP MOVSW, realicen una iteración en cada ciclo de reloj, mientras que el 80486 necesitaba tres relojes por iteración (y los primeros chips x86 significativamente más que el 486). Además, la optimización del acceso a las primeras palabras de microcódigo durante las etapas de decodificación ayuda a que varias instrucciones frecuentes se ejecuten significativamente más rápidamente, especialmente en sus formas más comunes y en casos típicos. Algunos ejemplos son (486 → Pentium, en ciclos de reloj): CALL (3 → 1), RET (5 → 2), cambia / rota (2–3 → 1).

- Un multiplicador más rápido, completamente basado en hardware, hace que las instrucciones como MUL e IMUL sean varias veces más rápidas (y más predecibles) que en el 80486; el tiempo de ejecución se reduce de 13 a 42 ciclos de reloj a 10-11 para operandos de 32 bits.

- Interrupción virtualizada para acelerar el modo 8086 virtual .

- Predicción de rama

-

Otras caracteristicas :

- Funciones de depuración mejoradas con la introducción del puerto de depuración basado en procesador (consulte Depuración del procesador Pentium en el Manual para desarrolladores, Vol 1).

- Funciones de autoprueba mejoradas como la verificación de paridad de caché L1 (consulte Estructura de caché en el Manual de desarrolladores, Vol 1).

- Nuevas instrucciones: CPUID, CMPXCHG8B, RDTSC, RDMSR, WRMSR, RSM.

- Se eliminaron los registros de prueba TR0 – TR7 y las instrucciones MOV para acceder a ellos.

- El Pentium MMX posterior también agregó el conjunto de instrucciones MMX , una extensión básica de conjunto de instrucciones de instrucción única de entero y datos múltiples ( SIMD ) comercializada para su uso en aplicaciones multimedia . MMX no se pudo usar simultáneamente con las instrucciones x87 FPU porque los registros se reutilizaron (para permitir cambios de contexto rápidos). Las mejoras más importantes fueron la duplicación de los tamaños de caché de datos e instrucciones y algunos cambios de microarquitectura para un mejor rendimiento.

El Pentium fue diseñado para ejecutar más de 100 millones de instrucciones por segundo (MIPS), y el modelo de 75 MHz pudo alcanzar 126.5 MIPS en ciertos puntos de referencia. La arquitectura Pentium generalmente ofrecía poco menos del doble del rendimiento de un procesador 486 por ciclo de reloj en los puntos de referencia comunes. Las piezas 80486 más rápidas (con una microarquitectura ligeramente mejorada y un funcionamiento a 100 MHz) eran casi tan potentes como los Pentium de primera generación, y el AMD Am5x86 era aproximadamente igual al Pentium 75 en cuanto al rendimiento de ALU puro.

Errata

Las primeras versiones de Pentiums P5 de 60–100 MHz tenían un problema en la unidad de punto flotante que daba como resultado resultados incorrectos (pero predecibles) de algunas operaciones de división. Esta falla, descubierta en 1994 por el profesor Thomas Nicely en Lynchburg College, Virginia, se hizo ampliamente conocida como la falla Pentium FDIV y causó vergüenza a Intel, que creó un programa de intercambio para reemplazar los procesadores defectuosos.

En 1997, se descubrió otra errata que podría permitir que un programa malicioso bloqueara un sistema sin privilegios especiales, el " error F00F ". Todos los procesadores de la serie P5 se vieron afectados y nunca se lanzaron versiones fijas; sin embargo, los sistemas operativos contemporáneos fueron parcheados con soluciones para evitar fallas.

Núcleos y pasos

El Pentium fue el microprocesador principal de Intel para computadoras personales a mediados de la década de 1990. El diseño original se volvió a implementar en procesos más nuevos y se agregaron nuevas características para mantener su competitividad y para abordar mercados específicos como las computadoras portátiles. Como resultado, hubo varias variantes de la microarquitectura P5.

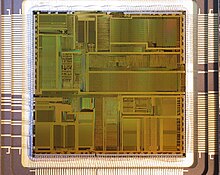

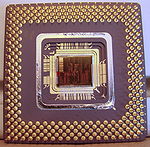

P5

El primer núcleo del microprocesador Pentium recibió el nombre en código "P5". Su código de producto era 80501 (80500 para los primeros pasos Q0399). Había dos versiones, especificadas para operar a 60 MHz y 66 MHz respectivamente, usando Socket 4 . Esta primera implementación del Pentium utilizó una fuente de alimentación tradicional de 5 voltios (descendiente de los requisitos habituales de compatibilidad de lógica transistor-transistor (TTL)). Contenía 3,1 millones de transistores y medía 16,7 mm por 17,6 mm para un área de 293,92 mm 2 . Se fabricó en un proceso de semiconductor de óxido de metal complementario bipolar ( BiCMOS ) de 0,8 μm . El diseño de 5 voltios resultó en un consumo de energía relativamente alto para su frecuencia de operación en comparación con los modelos siguientes.

P54C

El P5 fue seguido por el P54C (80502) en 1994, con versiones especificadas para operar a 75, 90 o 100 MHz utilizando una fuente de alimentación de 3,3 voltios. Marcando el cambio a Socket 5 , este fue el primer procesador Pentium en operar a 3.3 voltios, reduciendo el consumo de energía, pero requiriendo regulación de voltaje en las placas base. Al igual que con los procesadores 486 de mayor frecuencia, se empleó un multiplicador de reloj interno a partir de ahora para permitir que los circuitos internos funcionen a una frecuencia más alta que la dirección externa y los buses de datos, ya que es más complicado y engorroso aumentar la frecuencia externa, debido a limitaciones físicas. También permitía el multiprocesamiento bidireccional y tenía un APIC local integrado y nuevas funciones de administración de energía. Contenía 3,3 millones de transistores y medía 163 mm 2 . Se fabricó en un proceso BiCMOS que se ha descrito como 0,5 μm y 0,6 μm debido a las diferentes definiciones.

P54CQS

El P54C fue seguido por el P54CQS a principios de 1995, que operaba a 120 MHz. Se fabricó en un proceso BiCMOS de 0,35 μm y fue el primer microprocesador comercial que se fabricó en un proceso de 0,35 μm. Su recuento de transistores es idéntico al del P54C y, a pesar del proceso más nuevo, también tenía un área de troquel idéntica. El chip se conectó al paquete mediante unión de cables , que solo permite conexiones a lo largo de los bordes del chip. Un chip más pequeño habría requerido un rediseño del paquete, ya que existe un límite en la longitud de los cables y los bordes del chip estarían más alejados de las almohadillas del paquete. La solución fue mantener el chip del mismo tamaño, retener el anillo de almohadilla existente y solo reducir el tamaño de los circuitos lógicos del Pentium para permitirle alcanzar frecuencias de reloj más altas.

P54CS

El P54CQS fue seguido rápidamente por el P54CS, que operaba a 133, 150, 166 y 200 MHz, e introdujo el Socket 7 . Contenía 3,3 millones de transistores, medía 90 mm 2 y se fabricó en un proceso BiCMOS de 0,35 μm con cuatro niveles de interconexión.

P24T

El P24T Pentium OverDrive para sistemas 486 se lanzó en 1995, que se basaba en versiones de 3,3 V 0,6 μm con un reloj de 63 u 83 MHz. Dado que estos utilizado Socket de 2 / 3 , algunas modificaciones se tuvieron que hacer para compensar el bus de datos de 32 bits y más lento caché L2 de a bordo de 486 placas base. Por lo tanto, estaban equipados con una caché L1 de 32 KB (el doble que las CPU Pentium anteriores a P55C).

P55C

El P55C (o 80503) fue desarrollado por el Centro de Investigación y Desarrollo de Intel en Haifa, Israel . Se vendió como Pentium con tecnología MMX (generalmente llamado Pentium MMX ); aunque se basaba en el núcleo P5, presentaba un nuevo conjunto de 57 instrucciones "MMX" destinadas a mejorar el rendimiento en tareas multimedia, como la codificación y decodificación de datos de medios digitales. La línea Pentium MMX se introdujo el 22 de octubre de 1996 y se lanzó en enero de 1997.

Las nuevas instrucciones funcionaron en nuevos tipos de datos: vectores empaquetados de 64 bits de ocho enteros de 8 bits, cuatro enteros de 16 bits, dos enteros de 32 bits o un entero de 64 bits. Entonces, por ejemplo, la instrucción PADDUSB (Packed ADD Unsigned Saturated Byte) agrega dos vectores, cada uno de los cuales contiene ocho enteros de 8 bits sin signo juntos, por elementos; cada adición que se desbordaría se satura , produciendo 255, el valor máximo sin signo que se puede representar en un byte. Estas instrucciones bastante especializadas generalmente requieren una codificación especial por parte del programador para su uso.

Otros cambios en el núcleo incluyen una canalización de 6 etapas (frente a 5 en P5) con una pila de retorno (realizada por primera vez en Cyrix 6x86) y mejor paralelismo, un decodificador de instrucciones mejorado, caché de datos L1 de 16 KB + caché de instrucciones L1 de 16 KB con ambos 4 asociatividad de vías (frente a datos / instrucción de 8KB L1 con 2 vías en P5), 4 búferes de escritura que ahora podrían ser utilizados por cualquier tubería (frente a uno correspondiente a cada tubería en P5) y un predictor de rama mejorado tomado del Pentium Pro, con un búfer de 512 entradas (frente a 256 en P5).

Contenía 4,5 millones de transistores y tenía un área de 140 mm 2 . Fue fabricado en un proceso CMOS de 0,28 μm con los mismos pasos de metal que el proceso BiCMOS de 0,35 μm anterior, por lo que Intel lo describió como "0,35 μm" debido a su densidad de transistores similar. El proceso tiene cuatro niveles de interconexión.

Si bien el P55C siguió siendo compatible con Socket 7 , los requisitos de voltaje para alimentar el chip difieren de las especificaciones estándar del Socket 7. La mayoría de las placas base fabricadas para Socket 7 antes del establecimiento del estándar P55C no cumplen con el riel de voltaje dual requerido para el funcionamiento adecuado de esta CPU (voltaje de núcleo de 2,9 voltios, voltaje de entrada / salida (E / S) de 3,3 voltios ). Intel abordó el problema con los kits de actualización OverDrive que incluían un intercalador con su propia regulación de voltaje.

Tillamook

Las CPU de los portátiles Pentium MMX utilizaban un módulo móvil que contenía la CPU. Este módulo era una placa de circuito impreso (PCB) con la CPU directamente conectada a él en un factor de forma más pequeño. El módulo se encajó a presión en la placa base del portátil y, por lo general, se instaló un esparcidor de calor que hizo contacto con el módulo. Sin embargo, con el Tillamook Mobile Pentium MMX de 0,25 μm (que lleva el nombre de una ciudad de Oregón ), el módulo también contenía el chipset 430TX junto con la memoria caché de memoria estática de acceso aleatorio (SRAM) de 512 KB del sistema .

Modelos y variantes

|

|

|

||||||||||||||||||||

| Nombre clave | P5 | P54C | P54C / P54CQS | P54CS | P55C | Tillamook | ||||||||||||||||

| Código de producto | 80501 | 80502 | 80503 | |||||||||||||||||||

| Tamaño de proceso ( μm ) | 0,80 | 0,60 o 0,35 * | 0,35 | 0.35 (luego 0.28) | 0,25 | |||||||||||||||||

| Área de matriz ( mm 2 ) | 293,92 (16,7 x 17,6 mm) | 148 @ 0,6 μm / 91 (luego 83) @ 0,35 μm | 91 (más tarde 83) | 141 a 0,35 μm / 128 a 0,28 μm | 94,47 (9,06272 x 10,42416 mm) | |||||||||||||||||

| Número de transistores (millones) | 3.10 | 3,20 | 3.30 | 4.50 | ||||||||||||||||||

| Enchufe | Zócalo 4 | Zócalo 5/7 | Toma 7 | |||||||||||||||||||

| Paquete | CPGA / CPGA + IHS | CPGA / CPGA + IHS / TCP * | CPGA / TCP * | CPGA / TCP * | CPGA / PPGA | PPGA | TCP * | CPGA / PPGA / TCP * | PPGA / TCP * | TCP / TCP en MMC-1 | ||||||||||||

| Velocidad de reloj ( MHz ) | 60 | 66 | 75 | 90 | 100 | 120 | 133 | 150 | 166 | 200 | 120 * | 133 * | 150 * | 166 | 200 | 233 | 166 | 200 | 233 | 266 | 300 | |

| Velocidad del bus ( MHz ) | 60 | 66 | 50 | 60 | 50 | 66 | 60 | 66 | 60 | 66 | 60 | 66 | 60 | 66 | ||||||||

| Voltaje del núcleo | 5,0 | 5.15 | 3,3 2,9 * | 3,3 2,9 * | 3,3 3,1 * 2,9 * | 3,3 3,1 * 2,9 * | 3,3 3,1 * 2,9 * | 3,3 3,1 * 2,9 * | 3.3 | 3.3 | 2,2 * | 2,45 * | 2,45 * | 2,8 2,45 * | 2.8 | 2.8 | 1,9 1,8 * | 1,8 * | 1,8 * | 1,9 2,0 * | 2,0 * | |

| Voltaje de E / S | 5,0 | 5.15 | 3.3 | 3.3 | 3.3 | 3.3 | 3.3 | 3.3 | 3.3 | 3.3 | 3.3 | 3.3 | 3.3 | 3.3 | 3.3 | 3.3 | 2.5 | 2.5 | 2.5 | 2.5 | 2.5 | |

| TDP (máx. W) | 14,6 (15,3) | 16,0 (17,3) | 8,0 (9,5) 6,0 * (7,3 *) | 9,0 (10,6) 7,3 * (8,8 *) | 10,1 (11,7) 8,0 a 0,6 μ * (9,8 a 0,6 μ *) 5,9 a 0,35 μ * (7,6 a 0,35 μ *) | 12,8 (13,4) 7,1 * (8,8 *) | 11,2 (12,2) 7,9 * (9,8 *) | 11,6 (13,9) 10,0 * (12,0 *) | 14,5 (15,3) | 15,5 (16,6) | 4,2 * | 7,8 * (11,8 *) | 8,6 * (12,7 *) | 13,1 (15,7) 9,0 * (13,7 *) | 15,7 (18,9) | 17,0 (21,5) | 4,5 (7,4) 4,1 * (5,4 *) | 5,0 * (6,1 *) | 5,5 * (7,0 *) | 7,6 (9,2) 7,6 * (9,6 *) | 8.0 * | |

| Introducido | 1993-03-22 | 1994-10-10 | 1994-03-07 | 1995-03-27 | 1995-06-12 | 1996-01-04 | 1996-06-10 | 1997-10-20 | 1997-05-19 | 1997-01-08 | 1997-06-02 | 1997-08 | 1998-01 | 1999-01 | ||||||||

| * Un asterisco indica que estos solo estaban disponibles como chips Mobile Pentium o Mobile Pentium MMX para computadoras portátiles . | ||||||||||||||||||||||

| Nombre clave | P54CTB | ||||||

|---|---|---|---|---|---|---|---|

| Código de producto | PODPMT60X150 | PODPMT66X166 | PODPMT60X180 | PODPMT66X200 | |||

| Tamaño de proceso (μm) | 0,35 | ||||||

| Enchufe | Zócalo 5/7 | ||||||

| Paquete | CPGA con disipador de calor, ventilador y regulador de voltaje | ||||||

| Velocidad de reloj (MHz) | 125 | 150 | 166 | 150 | 180 | 200 | |

| Velocidad del bus (MHz) | 50 | 60 | 66 | 50 | 60 | 66 | |

| Actualizar para | Pentium 75 | Pentium 90 | Pentium 100 y 133 | Pentium 75 | Pentium 90, 120 y 150 | Pentium 100, 133 y 166 | |

| TDP (máx. W) | 15,6 | 15,6 | 15,6 | 18 | |||

| Voltaje | 3.3 | 3.3 | 3.3 | 3.3 | |||

| Nombre clave | P55C | Tillamook | |||||

|---|---|---|---|---|---|---|---|

| Código de producto | FV8050366200 | FV8050366233 | FV80503CSM66166 | GC80503CSM66166 | GC80503CS166EXT | FV80503CSM66266 | GC80503CSM66266 |

| Tamaño de proceso ( μm ) | 0,35 | 0,25 | |||||

| Velocidad de reloj ( MHz ) | 200 | 233 | 166 | 166 | 166 | 266 | 266 |

| Velocidad del bus ( MHz ) | 66 | 66 | 66 | 66 | 66 | 66 | 66 |

| Paquete | PPGA | PPGA | PPGA | BGA | BGA | PPGA | BGA |

| TDP (máx. W) | 15,7 | 17 | 4.5 | 4.1 | 4.1 | 7,6 | 7,6 |

| Voltaje | 2.8 | 2.8 | 1,9 | 1.8 | 1.8 | 1,9 | 2.0 |

Competidores

Después de la introducción del Pentium, competidores como NexGen , AMD, Cyrix y Texas Instruments anunciaron procesadores compatibles con Pentium en 1994. La revista CIO identificó al Nx586 de NexGen como la primera CPU compatible con Pentium, mientras que PC Magazine describió al Cyrix 6x86 como el primero. . A estos le siguió el AMD K5 , que se retrasó debido a dificultades de diseño. AMD luego compró NexGen para ayudar a diseñar el AMD K6 , y National Semiconductor compró Cyrix . Los procesadores posteriores de AMD e Intel conservan la compatibilidad con el Pentium original.

Ver también

- Lista de microarquitecturas de CPU Intel

- Lista de microprocesadores Intel Pentium

- Caché en un dispositivo (COASt), módulos de caché L2 para Pentium

- Arquitectura de conjunto de instrucciones IA-32 (ISA)

- Controlador de caché Intel 82497

Competidores

Referencias

enlaces externos

- CPU-Collection.de - Imágenes y descripciones de Intel Pentium

- Identificación de CPU Intel en línea de plasma

- The Pentium Timeline Project El Pentium Timeline Project mapea el chip más antiguo y el más joven conocido de cada s-spec fabricado. Los datos se muestran en una línea de tiempo interactiva.

Hojas de datos de Intel

- Pentium (P5)

- Pentium (P54)

- Pentium MMX (P55C)

- Pentium MMX móvil (P55C)

- Pentium MMX móvil (Tillamook)

Manuales de Intel

Estos manuales proporcionan una descripción general del procesador Pentium y sus características:

- Familia de procesadores Pentium Manual del desarrollador Procesador Pentium (Volumen 1) (Número de pedido Intel 241428)

- Manual del desarrollador de la familia de procesadores Pentium Volumen 2: Referencia del conjunto de instrucciones (Número de pedido Intel 243191)

- Manual del desarrollador de la familia de procesadores Pentium Volumen 3: Manual de programación y arquitectura (Número de pedido Intel 241430)