Multithreading (arquitectura de computadora) - Multithreading (computer architecture)

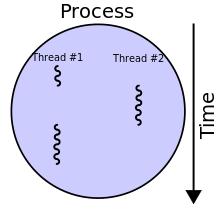

En la arquitectura de la computadora , el subproceso múltiple es la capacidad de una unidad central de procesamiento (CPU) (o un solo núcleo en un procesador de múltiples núcleos ) para proporcionar múltiples subprocesos de ejecución al mismo tiempo, respaldados por el sistema operativo . Este enfoque difiere del multiprocesamiento . En una aplicación multiproceso, los subprocesos comparten los recursos de uno o varios núcleos, que incluyen las unidades informáticas, las memorias caché de la CPU y el búfer de búsqueda de traducción (TLB).

Cuando los sistemas de multiprocesamiento incluyen múltiples unidades de procesamiento completas en uno o más núcleos, el multiproceso tiene como objetivo aumentar la utilización de un solo núcleo mediante el uso de paralelismo a nivel de subprocesos , así como paralelismo a nivel de instrucción . Como las dos técnicas son complementarias, se combinan en casi todas las arquitecturas de sistemas modernos con múltiples CPU de subprocesos múltiples y con CPU con múltiples núcleos de subprocesos múltiples.

Descripción general

El paradigma de subprocesos múltiples se ha vuelto más popular a medida que los esfuerzos para explotar aún más el paralelismo a nivel de instrucción se han estancado desde finales de la década de 1990. Esto permitió que el concepto de la computación de rendimiento resurgiera del campo más especializado del procesamiento de transacciones . Aunque es muy difícil acelerar aún más un solo hilo o un solo programa, la mayoría de los sistemas informáticos son en realidad multitarea entre varios hilos o programas. Por lo tanto, las técnicas que mejoran el rendimiento de todas las tareas dan como resultado ganancias de rendimiento general.

Dos técnicas principales para la computación de rendimiento son el multiproceso y el multiprocesamiento .

Ventajas

Si un subproceso tiene muchos errores de caché , los otros subprocesos pueden continuar aprovechando los recursos informáticos no utilizados, lo que puede conducir a una ejecución general más rápida, ya que estos recursos habrían estado inactivos si solo se hubiera ejecutado un solo subproceso. Además, si un subproceso no puede utilizar todos los recursos informáticos de la CPU (porque las instrucciones dependen del resultado de cada uno), ejecutar otro subproceso puede evitar que esos recursos se queden inactivos.

Desventajas

Varios subprocesos pueden interferir entre sí al compartir recursos de hardware, como cachés o búferes de búsqueda de traducción (TLB). Como resultado, los tiempos de ejecución de un solo subproceso no mejoran y pueden degradarse, incluso cuando solo se está ejecutando un subproceso, debido a frecuencias más bajas o etapas de canalización adicionales que son necesarias para acomodar el hardware de conmutación de subprocesos.

La eficiencia general varía; Intel afirma una mejora de hasta un 30% con su tecnología Hyper-Threading , mientras que un programa sintético que solo realiza un ciclo de operaciones de punto flotante dependientes no optimizadas en realidad obtiene una mejora de velocidad del 100% cuando se ejecuta en paralelo. Por otro lado, los programas en lenguaje ensamblador ajustados a mano que usan extensiones MMX o AltiVec y realizan búsquedas previas de datos (como podría hacerlo un buen codificador de video) no sufren pérdidas de caché o recursos informáticos inactivos. Por lo tanto, dichos programas no se benefician del subproceso múltiple de hardware y, de hecho, pueden ver un rendimiento degradado debido a la contención de recursos compartidos.

Desde el punto de vista del software, el soporte de hardware para multiprocesamiento es más visible para el software, lo que requiere más cambios en los programas de aplicación y los sistemas operativos que el multiprocesamiento. Las técnicas de hardware utilizadas para admitir subprocesos múltiples a menudo son paralelas a las técnicas de software utilizadas para la multitarea informática . La programación de subprocesos también es un problema importante en el subproceso múltiple.

Tipos de subprocesos múltiples

Múltiples subprocesos intercalados / temporales

Subprocesos múltiples de grano grueso

El tipo más simple de subprocesos múltiples ocurre cuando un subproceso se ejecuta hasta que es bloqueado por un evento que normalmente crearía un bloqueo de latencia prolongada. Tal bloqueo podría ser una falta de caché que tiene que acceder a la memoria fuera del chip, lo que puede tomar cientos de ciclos de CPU para que los datos regresen. En lugar de esperar a que se resuelva el bloqueo, un procesador de subprocesos cambiaría la ejecución a otro subproceso que estaba listo para ejecutarse. Solo cuando los datos del hilo anterior hubieran llegado, el hilo anterior se volvería a colocar en la lista de hilos listos para ejecutar .

Por ejemplo:

- Ciclo i : se emite la instrucción j del hilo A.

- Ciclo i + 1 : se emite la instrucción j + 1 del hilo A.

- Ciclo i + 2 : se emite la instrucción j + 2 del subproceso A , que es una instrucción de carga que falla en todos los cachés.

- Ciclo i + 3 : programador de subprocesos invoca, interruptores para enhebrar B .

- Ciclo i + 4 : se emite la instrucción k del hilo B.

- Ciclo i + 5 : se emite la instrucción k + 1 del hilo B.

Conceptualmente, es similar a la multitarea cooperativa utilizada en sistemas operativos en tiempo real , en la que las tareas renuncian voluntariamente al tiempo de ejecución cuando necesitan esperar algún tipo de evento. Este tipo de subprocesos múltiples se conoce como subprocesos múltiples en bloque, cooperativos o de grano grueso.

El objetivo del soporte de hardware de subprocesos múltiples es permitir un cambio rápido entre un subproceso bloqueado y otro subproceso listo para ejecutarse. Para lograr este objetivo, el costo del hardware es replicar los registros visibles del programa, así como algunos registros de control del procesador (como el contador del programa). Cambiar de un hilo a otro significa que el hardware cambia de usar un conjunto de registros a otro; para cambiar de manera eficiente entre subprocesos activos, cada subproceso activo debe tener su propio conjunto de registros. Por ejemplo, para cambiar rápidamente entre dos subprocesos, el hardware del registro debe crearse dos veces.

El soporte de hardware adicional para múltiples subprocesos permite que la conmutación de subprocesos se realice en un ciclo de CPU, lo que brinda mejoras de rendimiento. Además, el hardware adicional permite que cada subproceso se comporte como si se ejecutara solo y no compartiera ningún recurso de hardware con otros subprocesos, lo que minimiza la cantidad de cambios de software necesarios dentro de la aplicación y el sistema operativo para admitir subprocesos múltiples.

Muchas familias de microcontroladores y procesadores integrados tienen múltiples bancos de registros para permitir un cambio de contexto rápido para las interrupciones. Dichos esquemas pueden considerarse un tipo de subproceso múltiple de bloques entre el subproceso del programa de usuario y los subprocesos de interrupción.

Multihilo intercalado

El propósito del subproceso múltiple intercalado es eliminar todos los bloqueos de dependencia de datos de la canalización de ejecución . Dado que un subproceso es relativamente independiente de otros subprocesos, hay menos posibilidades de que una instrucción en una etapa de canalización necesite una salida de una instrucción anterior en el canal. Conceptualmente, es similar a la multitarea preventiva que se usa en los sistemas operativos; una analogía sería que el intervalo de tiempo dado a cada subproceso activo es un ciclo de CPU.

Por ejemplo:

- Ciclo i + 1 : se emite una instrucción desde el hilo B.

- Ciclo i + 2 : se emite una instrucción desde el hilo C.

Este tipo de subprocesamiento múltiple se denominó primero procesamiento de barril, en el que las duelas de un barril representan las etapas de la tubería y sus hilos de ejecución. El subproceso múltiple intercalado, preventivo, de grano fino o dividido en el tiempo es una terminología más moderna.

Además de los costos de hardware discutidos en el tipo de bloque de subprocesamiento múltiple, el subproceso múltiple intercalado tiene un costo adicional de que cada etapa de canalización rastree el ID de subproceso de la instrucción que está procesando. Además, dado que hay más subprocesos que se ejecutan al mismo tiempo en la canalización, los recursos compartidos, como cachés y TLB, deben ser más grandes para evitar que se produzcan errores entre los diferentes subprocesos.

Subprocesos múltiples simultáneos

El tipo más avanzado de subprocesos múltiples se aplica a los procesadores superescalares . Mientras que un procesador superescalar normal emite varias instrucciones desde un único subproceso en cada ciclo de la CPU, en el subproceso múltiple simultáneo (SMT) un procesador superescalar puede emitir instrucciones desde varios subprocesos en cada ciclo de la CPU. Reconociendo que cualquier subproceso tiene una cantidad limitada de paralelismo a nivel de instrucción , este tipo de subprocesos múltiples intenta explotar el paralelismo disponible en varios subprocesos para disminuir el desperdicio asociado con los espacios de problemas no utilizados.

Por ejemplo:

- Ciclo i : las instrucciones j y j + 1 del hilo A y la instrucción k del hilo B se emiten simultáneamente.

- Ciclo i + 1 : la instrucción j + 2 del hilo A , la instrucción k + 1 del hilo B y la instrucción m del hilo C se emiten todas simultáneamente.

- Ciclo i + 2 : la instrucción j + 3 del hilo A y las instrucciones m + 1 y m + 2 del hilo C se emiten todas simultáneamente.

Para distinguir los otros tipos de subprocesos múltiples de SMT, el término " subprocesos múltiples temporales " se utiliza para indicar cuándo se pueden emitir instrucciones de un solo subproceso a la vez.

Además de los costos de hardware discutidos para el subproceso múltiple intercalado, SMT tiene el costo adicional de cada etapa de canalización que rastrea el ID de subproceso de cada instrucción que se procesa. Nuevamente, los recursos compartidos como cachés y TLB deben dimensionarse para la gran cantidad de subprocesos activos que se procesan.

Las implementaciones incluyen DEC (más tarde Compaq ) EV8 (no completado), tecnología Intel Hyper-Threading , IBM POWER5 / POWER6 / POWER7 / POWER8 / POWER9 , IBM z13 / z14 / z15 , Sun Microsystems UltraSPARC T2 , Cray XMT y AMD Bulldozer y Zen microarquitecturas.

Detalles de implementación

Un área importante de investigación es el programador de subprocesos que debe elegir rápidamente entre la lista de subprocesos listos para ejecutar para ejecutar a continuación, así como mantener las listas de subprocesos listos para ejecutar y detenidos. Un subtema importante son los diferentes esquemas de prioridad de subprocesos que puede utilizar el planificador. El programador de subprocesos puede implementarse totalmente en software, totalmente en hardware o como una combinación de hardware / software.

Otra área de investigación es qué tipo de eventos deberían causar un cambio de hilo: fallas de caché, comunicación entre hilos, finalización de DMA , etc.

Si el esquema de subprocesos múltiples replica todo el estado visible del software, incluidos los registros de control privilegiados y TLB, entonces permite que se creen máquinas virtuales para cada subproceso. Esto permite que cada subproceso ejecute su propio sistema operativo en el mismo procesador. Por otro lado, si solo se guarda el estado del modo de usuario, entonces se requiere menos hardware, lo que permitiría que haya más subprocesos activos al mismo tiempo por el mismo área de matriz o costo.

Ver también

Referencias

enlaces externos

- Una encuesta de procesadores con multiproceso explícito , ACM , marzo de 2003, por Theo Ungerer, Borut Robi y Jurij Silc

- Sistema operativo | Diferencia entre GeeksforGeeks multitarea, multiproceso y multiprocesamiento , 6 de septiembre de 2018.