Taxonomía de Flynn - Flynn's taxonomy

La taxonomía de Flynn es una clasificación de arquitecturas de computadora , propuesta por Michael J. Flynn en 1966. y ampliada en 1972. El sistema de clasificación se ha estancado y se ha utilizado como herramienta en el diseño de procesadores modernos y sus funcionalidades. Desde el surgimiento de las unidades de procesamiento central de multiprocesamiento (CPU), un contexto de multiprogramación ha evolucionado como una extensión del sistema de clasificación. El procesamiento de vectores , cubierto por la taxonomía de Duncan , falta en el trabajo de Flynn porque el Cray-1 se lanzó en 1977: el segundo artículo de Flynn se publicó en 1972.

Clasificaciones

Las cuatro clasificaciones iniciales definidas por Flynn se basan en el número de secuencias de instrucciones (o control) concurrentes y secuencias de datos disponibles en la arquitectura. Más tarde, Flynn definió tres subcategorías adicionales de SIMD en 1972.

| Taxonomía de Flynn |

|---|

| Flujo de datos único |

| Múltiples flujos de datos |

| Subcategorías SIMD |

| Ver también |

Secuencia de instrucciones única, secuencia de datos única (SISD)

Una computadora secuencial que no explota paralelismo ni en la instrucción ni en los flujos de datos. La unidad de control única (CU) recupera el flujo de instrucciones único (IS) de la memoria. Entonces, la CU genera señales de control apropiadas para dirigir el elemento de procesamiento único (PE) para que opere en un flujo de datos único (DS), es decir, una operación a la vez.

Ejemplos de arquitectura SISD son las tradicionales máquinas monoprocesador como las computadoras personales más antiguas (PC; para 2010, muchas PC tenían múltiples núcleos) y computadoras mainframe .

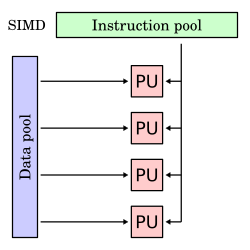

Secuencia de instrucciones única, secuencias de datos múltiples (SIMD)

Una sola instrucción se aplica simultáneamente a múltiples flujos de datos diferentes. Las instrucciones se pueden ejecutar secuencialmente, como por canalización, o en paralelo por múltiples unidades funcionales. El artículo de 1972 de Flynn subdividió SIMD en tres categorías más:

- Procesador de matriz : reciben la única (misma) instrucción, pero cada unidad de procesamiento paralelo tiene su propia memoria y archivo de registro separados y distintos.

- Procesador canalizado : reciben la única (misma) instrucción pero luego leen datos de un recurso central, cada uno procesa fragmentos de esos datos y luego escribe los resultados en el mismo recurso central. En la Figura 5 del artículo de Flynn de 1977, ese recurso es la memoria principal: para las CPU modernas, ese recurso ahora es más típicamente el archivo de registro.

- Procesador asociativo : reciben la única (misma) instrucción, pero en cada unidad de procesamiento paralelo se toma una decisión independiente , basada en los datos locales de la unidad, en cuanto a realizar la ejecución o omitirla. En la terminología moderna, esto se conoce como SIMD "predicado" (enmascarado).

Algunos diseños modernos ( GPU en particular) toman características de más de una de estas subcategorías: Las GPU de hoy son SIMT pero también son Asociativas, es decir, cada elemento de procesamiento en la matriz SIMT también está predicado.

Procesador de matriz

El término moderno para un procesador de matriz es instrucción única, múltiples subprocesos (SIMT). Ésta es una clasificación distinta en la taxonomía de 1972 de Flynn, como una subcategoría de SIMD. Es identificable por los subelementos paralelos que tienen su propio archivo de registro y memoria independientes (caché y memoria de datos). Los artículos originales de Flynn citan dos ejemplos históricos de procesadores SIMT: SOLOMON e ILLIAC IV

Nvidia comúnmente usa el término en sus materiales de marketing y documentos técnicos donde defiende la novedad de la arquitectura de Nvidia. SOLOMON es anterior a NVidia en más de 60 años.

El Aspex Microelectronics Associative String Processor (ASP) se clasificó a sí mismo en su material de marketing como "Massive wide SIMD" pero tenía ALU a nivel de bit y predicación a nivel de bit (Taxonomía de Flynn: Procesamiento asociativo) y cada uno de los procesadores 4096 tenía sus propios registros y memoria (taxonomía de Flynn: procesamiento de matrices). El Linedancer, lanzado en 2010, contenía 4096 ALU SIMD Predicadas de 2 bits, cada una con su propia Memoria Direccionable por Contenido , y era capaz de 800 mil millones de instrucciones por segundo. El procesador SIMT de matriz asociativa ASP de Aspex es anterior a NVIDIA en 20 años.

Procesador canalizado

En el momento en que Flynn escribió su artículo de 1972, muchos sistemas usaban la memoria principal como el recurso desde el cual las tuberías leían y escribían. Cuando el recurso del que todos los "pipelines" leen y escriben es el archivo de registro en lugar de la memoria principal, resultan variantes modernas de SIMD. Los ejemplos incluyen Altivec , NEON y AVX .

Un nombre alternativo para este tipo de SIMD basado en registros es "SIMD empaquetada" y otro es SIMD dentro de un registro (SWAR) . Cuando se aplica la predicación, se convierte en procesamiento asociativo (abajo)

Procesador asociativo

El término moderno para Procesador asociativo es SIMD "predicado" (o enmascarado). Los ejemplos incluyen AVX-512 .

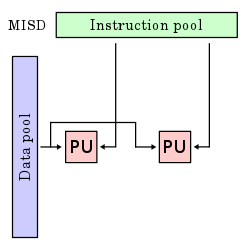

Múltiples flujos de instrucciones, flujo de datos único (MISD)

Varias instrucciones operan en un flujo de datos. Esta es una arquitectura poco común que generalmente se usa para tolerancia a fallas. Los sistemas heterogéneos operan en el mismo flujo de datos y deben estar de acuerdo con el resultado. Los ejemplos incluyen la computadora de control de vuelo del transbordador espacial .

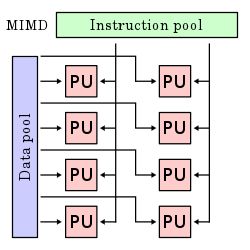

Múltiples flujos de instrucciones, múltiples flujos de datos (MIMD)

Múltiples procesadores autónomos que ejecutan simultáneamente diferentes instrucciones sobre diferentes datos. Las arquitecturas MIMD incluyen procesadores superescalares de múltiples núcleos y sistemas distribuidos , que utilizan un espacio de memoria compartida o un espacio de memoria distribuida.

Diagrama comparativo de clasificaciones

Estas cuatro arquitecturas se muestran a continuación visualmente. Cada unidad de procesamiento (PU) se muestra para una computadora uni-core o multi-core:

Más divisiones

A partir de 2006, las 10 mejores y la mayoría de las supercomputadoras TOP500 se basan en una arquitectura MIMD.

Aunque estos no son parte del trabajo de Flynn, algunos dividen aún más la categoría MIMD en las dos categorías siguientes, y a veces se consideran incluso más subdivisiones.

Programa único, múltiples flujos de datos (SPMD)

Múltiples procesadores autónomos que ejecutan simultáneamente el mismo programa (pero en puntos independientes, en lugar de en el mismo paso que impone SIMD) sobre diferentes datos. También denominado proceso único, datos múltiples : el uso de esta terminología para SPMD es técnicamente incorrecto, ya que SPMD es un modelo de ejecución paralela y asume que varios procesadores cooperan ejecutando un programa. SPMD es el estilo más común de programación paralela. El modelo SPMD y el término fueron propuestos por Frederica Darema del equipo RP3.

Múltiples programas, múltiples flujos de datos (MPMD)

Múltiples procesadores autónomos que operan simultáneamente al menos 2 programas independientes. Por lo general, estos sistemas eligen un nodo para que sea el "host" ("el modelo explícito de programación de host / nodo") o "administrador" (la estrategia "Administrador / Trabajador"), que ejecuta un programa que distribuye datos a todos los demás nodos. que todos ejecutan un segundo programa. A continuación, esos otros nodos devuelven sus resultados directamente al administrador. Un ejemplo de esto sería la consola de juegos Sony PlayStation 3, con su procesador SPU / PPU .

Ver también

- Taxonomía de Duncan

- Clasificación de Feng

- Händler 's Sistema de Clasificación de Erlangen (ECS)

- SWAR