POTENCIA2 - POWER2

| Información general | |

|---|---|

| Lanzado | 1993 |

| Diseñada por | IBM |

| Arquitectura y clasificación | |

| Conjunto de instrucciones | PODER ISA |

| Historia | |

| Predecesor | POTENCIA1 |

| Sucesor | POTENCIA3 |

| Arquitecturas POWER , PowerPC y Power ISA |

|---|

| NXP (anteriormente Freescale y Motorola) |

| IBM |

|

| IBM / Nintendo |

| Otro |

| Enlaces relacionados |

| Cancelado en gris , histórico en cursiva |

El POWER2 , originalmente llamado RIOS2 , es un procesador diseñado por IBM que implementó la arquitectura del conjunto de instrucciones POWER . El POWER2 fue el sucesor del POWER1 , debutando en septiembre de 1993 dentro de los sistemas RS / 6000 de IBM . Cuando se presentó, el POWER2 era el microprocesador más rápido, superando al Alpha 21064 . Cuando se introdujo el Alpha 21064A en 1993, el POWER2 perdió el liderazgo y se convirtió en el segundo. IBM afirmó que el rendimiento para un POWER2 de 62,5 MHz era 73,3 SPECint92 y 134,6 SPECfp92.

El compilador GCC de código abierto eliminó la compatibilidad con POWER1 (RIOS) y POWER2 (RIOS2) en la versión 4.5.

Descripción

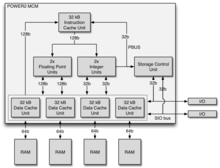

Mejoras sobre la POWER1 incluyen mejoras en la arquitectura del conjunto de instrucciones de potencia (que consisten en nuevas instrucciones del usuario y del sistema y otras funciones relacionadas con el sistema), velocidades de reloj más altas (55 a 71,5 MHz), un extra unidad de punto fijo y unidad de coma flotante , una más grande Caché de instrucciones de 32 KB y caché de datos más grande de 128 o 256 KB. El POWER2 era un diseño de varios chips que constaba de seis u ocho circuitos integrados semi-personalizados , dependiendo de la cantidad de caché de datos (la configuración de 256 KB requería ocho chips). La partición del diseño era idéntica a la del POWER1: un chip de unidad de caché de instrucciones, un chip de unidad de punto fijo, un chip de unidad de punto flotante, un chip de unidad de control de almacenamiento y dos o cuatro chips de unidad de caché de datos.

La configuración de ocho chips contiene un total de 23 millones de transistores y un área de matriz total de 1215 mm 2 . Los chips son fabricados por IBM en su proceso CMOS de 0,72 μm, que presenta una longitud de canal efectiva de 0,45 μm; y una capa de polisilicio y cuatro capas de metal se interconectan. Los chips están empaquetados en un módulo de múltiples chips de cerámica (MCM) que mide 64 mm por 64 mm.

POTENCIA2 +

En mayo de 1994 se introdujo una versión mejorada de POWER2 optimizada para el procesamiento de transacciones como POWER2 +. Las cargas de trabajo de procesamiento de transacciones se beneficiaron de la adición de una caché L2 con capacidades de 512 KB, 1 MB y 2 MB. Esta caché se implementó fuera del paquete con SRAM de ráfaga estándar de la industria. La caché se conectó al POWER2 + a través de un bus de 64 bits (para sistemas de gama baja) o de 128 bits (para sistemas de gama alta). La caché se asignó directamente , tenía un tamaño de línea de 128 bytes y era de escritura directa . Las etiquetas de caché estaban contenidas en el chip de la unidad de control de almacenamiento. El POWER2 + tiene un bus de memoria más estrecho de 64 o 128 bits y un caché de datos más pequeño de 64 o 128 KB. Como hay menos caché, los chips de la unidad de caché de datos son más pequeños como resultado, y el chip de la unidad de control de almacenamiento revisado también es más pequeño. Un objetivo de la configuración de seis chips era reducir el costo y, por lo tanto, los chips se empaquetan en un paquete de conexión de bola de soldadura (SBC) en lugar de un MCM.

P2SC

El P2SC, para POWER2 Super Chip , fue lanzado en octubre de 1996 como el sucesor del POWER2. Era una implementación de un solo chip del POWER2 de ocho chips, que integraba 15 millones de transistores en una matriz de 335 mm 2 fabricada en el proceso CMOS-6S de metal de cinco capas de 0,29 μm de IBM. La primera versión funcionó a 120 o 135 MHz, casi el doble de rápido que el POWER2 a 71,5 MHz, con la memoria y los buses de E / S funcionando a la mitad de la velocidad para admitir la frecuencia de reloj más alta. IBM afirmó que el rendimiento de esta versión era 5.5 SPECint95_base y 14.5 SPECfp95_base. En el Foro de Microprocesadores en octubre de 1997 se anunció una pieza más rápida de 160 MHz fabricada en el proceso CMOS-6S2 de 0,25 μm.

El P2SC no era una copia completa del POWER2, la caché de datos L1 y las capacidades del búfer de búsqueda de datos de traducción (TLB) se redujeron a la mitad a 128 KB y 256 entradas, respectivamente, y una característica que rara vez se usaba que bloqueaba las entradas en el TLB no se implementó en para ajustar el diseño original en un solo troquel.

El P2SC fue reemplazado por el POWER3 como el microprocesador insignia de IBM en la línea RS / 6000 en 1998. Un uso notable del P2SC fue el superordenador IBM Deep Blue de 30 nodos que venció al campeón mundial Garry Kasparov en el ajedrez en 1997. Sin embargo, la computadora Las capacidades de juego de ajedrez se debieron a sus circuitos integrados personalizados, en lugar de a los P2SC.

Ver también

- Arquitectura del conjunto de instrucciones de IBM POWER

- Microprocesadores IBM POWER

- POTENCIA1

- POTENCIA3

Notas

Referencias

- Barreh, JI; Golla, RT; Arimilli, LB; Jordan, PJ (septiembre de 1994). "Unidad de caché de instrucciones POWER2". IBM Journal of Research and Development . 38 (5): 537–544. doi : 10.1147 / rd.385.0537 .

- Ball, Richard (15 de octubre de 1997). "Chipville Estados Unidos". Electrónica semanal .

- DeTar, Jim (22 de agosto de 1994). "IBM detalla Power2 +; DEC descubre nuevo Alpha AXP". Noticias electrónicas .

- Gwennap, Linley (4 de octubre de 1993). "IBM recupera el liderazgo de rendimiento con Power2". Informe del microprocesador .

- Gwennap, Linley (26 de agosto de 1996). "IBM Crams POWER2 en un solo chip". Informe del microprocesador .

- Hicks, TN; Fry, RE; Harvey, PE (septiembre de 1994). "Unidad de coma flotante POWER2: Arquitectura e implementación". IBM Journal of Research and Development . 38 (5): 525–536. doi : 10.1147 / rd.385.0525 .

- Lineback, J. Robert (28 de junio de 1993). "IBM prepara RISC Progeny en Unix" . Noticias electrónicas .

- Shippy, David (9 de agosto de 1994). "El procesador Power2 +". Chips calientes 6 .

- Shippy, DJ; Griffith, TW (septiembre de 1994). "Unidades de control de almacenamiento, caché de datos y punto fijo POWER2". IBM Journal of Research and Development . 38 (5): 503–524. doi : 10.1147 / rd.385.0503 .

- Statt, Paul (enero de 1994). "Power2 toma la iniciativa, por ahora". Byte .

- Blanco, SW; Dhawan, S. (septiembre de 1994). "POWER2: Próxima generación de la familia RISC System / 6000". IBM Journal of Research and Development . 38 (5): 493–502. doi : 10.1147 / rd.385.0493 .

Otras lecturas

- Weiss, Shlomo; Smith, James Edward (1994). POWER y PowerPC . Morgan Kaufmann. ISBN 1558602798. - El Capítulo 6 describe la arquitectura y el procesador de POWER2